Unified Modeling, Automated Configuration and Simulation for Embedded Networks and Real-Time Software in a Single Platform

RTaW-Pegase supports the design of safe and optimized networks including automotive, aerospace, industrial Ethernet and TSN networks, CAN (FD,XL), LIN, Arinc and wireless networks. Pegase speeds-up the design exploration, optimization and validation of next-generation Software-Defined Systems. In addition to timing-accurate simulation, Pegase computes precise upper bounds on communication delays and buffer usage, and offers advanced automated configuration algorithms to ensure the correctness and efficient use of hardware and software components.

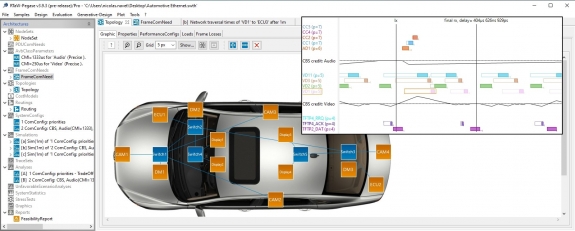

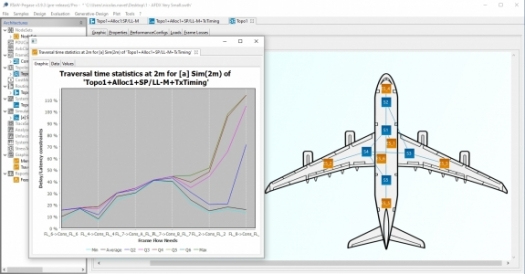

Network Topologies and Data Streams in RTaW-Pegase: Automotive Ethernet TSN backbone connected to CAN networks, hierarchical TSN-based industrial communication architecture, large AFDX network with switches forming a central backbone, NOC for manycore SoCs, and aerospace mesh network with triple redundant routing.

How RTaW-Pegase Enhances Your Network Design?

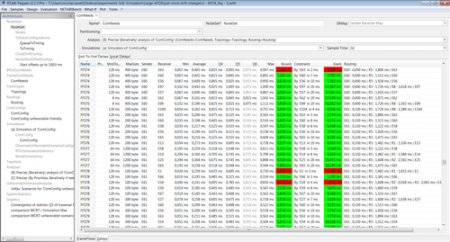

- Evidence-Based Design — RTaW-Pegase provides detailed performance metrics, including network loads, response times, jitters, and buffer usage, allowing you to predict system performance across various scenarios. The tool also offers features to compare different design and configuration options, supporting you throughout the entire development cycle.

Reduce Time-to-Market — Our proprietary ZeroConfig-TSN® (ZCT) generative design algorithm accelerates TSN network design by up to 30 times or more. Want to see ZCT in action? Contact the product manager for a demo.

- Cost Optimization: — RTaW-Pegase enables you to avoid over-provisioning of resources (processors, link speeds, memory in switches, unneeded technologies, etc). In addition, RTaW-Pegase includes design space exploration algorithms to optimize network topologies (e.g., number and location of switches), data streams routing and allocation of the software functions on the stations. Cost-performance trade-offs can be compared using built-in cost models – refer to this study for an example.

- Future-Proof Design — Our Topology Stress Test® (TST) function predicts how much traffic your network can handle, helping you design for future scalability. Interested in discovering how TST can assist in creating a future-proof network? Contact the product manager for a demo or download this study.

Results You Can Trust — RTaW-Pegase uses Network Calculus for timing verification, a method accepted in aeronautics certification. The core algorithms are detailed in peer-reviewed scientific publications — explore publications co-authored with our partners and research papers by our team members.

- Proven Track Record — Since 2008, leading companies in automotive, aerospace, and industrial sectors have trusted RTaW-Pegase – see the companies that rely on us for their critical network design needs.

Modelling, Configuration, Visualisation, Design-Space Exploration

Built-in support for variant management and comparison of design alternatives based on performance and cost

The results panel displays the calculated maximum communication latencies, with red indicating a timing constraint violation for a specific data flow. Zero-Config TSN® offers solutions to resolve these issues.

Key Features

Comprehensive Ethernet Support: Supports automotive, aerospace, and industrial Ethernet, including 802.1Q TSN, 802.1Qav/AVB Credit-Based Shaper, 802.1Qbv Time-Aware Shaper, 802.1Qcr Asynchronous Traffic Shaper, 802.1Qbu frame preemption, 802.1CB frame replication, 802.1Qci filtering, 802.1AS-2020 clock synchronization, 10BASE-T1S, SOME/TP (TP), DDS, DoIP, and AVTP. Also supports Time-Triggered Ethernet (SAE AS6802) and AFDX (ARINC664) for arbitrary speeds and topologies.

Performance Evaluation of Heterogenous Architectures: worst-case analysis and timing-accurate simulation of communication architectures composed of CAN (2.0A, 2.0B, CAN FD, CAN XL, and ARINC825), switched Ethernet, AFDX, TTE, FlexRay, LIN, PON (ETA 2024/10), ARINC429 and wireless networks such as 802.11p, interconnected through gateways.

Service-Oriented Communications with SOME/IP, DDS and MQTT (ETA2024/11), combined with dedicated TSN configuration algorithms, ensures reliable and timely delivery of services.

Support for Diverse Traffic Patterns: Handles periodic and sporadic message transmission patterns, UDP and TCP transmissions, segmented messages (e.g., video streams and FTP traffic), and complex transmission patterns (e.g., DoIp protocol, patterns defined via Java plugin).

Comprehensive Support for Timing and Reliability QoS: Supports FIFO, priority, AVB credit-based shaper, TSN time-aware shaper, frame preemption, Asynchronous Traffic Shapers, traffic policing (PSFP, IEEE802.1Qci), frame replication (FRER, IEEE802.11CB), TTEthernet (SAE AS6802) and round-robin frame schedulers.

Optimized Scheduling for TSN: Provides optimized transmission schedules for TSN Time-Aware Shaper (IEEE 802.11Qbv), meeting stringent timing constraints.

Comprehensive Performance Prediction: Offers both worst-case analysis and timing-accurate simulations, with a parallelized engine to predict worst-case and typical performance scenarios.

Modeling workbench featuring a robust graphical editing and visualization environment, a communication architecture editor, Gantt charts for communication traces, and tools for visually comparing design options.

System-Level Modeling: The Software-Defined Vehicles (SDV) module enables modeling, simulation, and worst-case schedulability analysis of software components on multi-core processors. System-level timing chains can be visualized via Gantt charts.

Trace Analysis (TraceInspector module): Supports PCAP(-NG) format for Ethernet and CANanalyzer format for CAN, detects non-conformance to specifications (such as packet size, transmission period, and unknown packets), validates modeling assumptions for event-triggered frames, estimates switching delays and successive frame inter-arrival times, and offers GANTT chart representations of the trace.

ZeroConfig-TSN (ZCT)Ⓒ: a “push-button” approach to automate the selection and configuration of TSN networks.

Design-Space Exploration: Topology Stress Test (TST)Ⓒ facilitates early-stage design decisions without full knowledge of communication requirements, allowing for exploration of topological and technological choices.

Optimized Configuration Algorithms: Includes optimized priority allocation and routing algorithms, configuration algorithms for AVB credit-based shaper, TSN time-aware shaper and the asynchronous traffic shaper.

Accurate Latency Computations: Maximum pessimism of computed communication latencies to typically less than 15% compared to true worst-case latencies.

Fast and Efficient: Analyzes and simulates large networks in seconds, providing quick insights for complex systems.

- State-of-the-Art Network Calculus: Uses advanced Network Calculus techniques to compute upper bounds on communication latencies, frame jitters, and buffer utilization (see our research works on Network Calculus here).

Task Scheduling Analysis: Supports the configuration and analysis of task scheduling, including Event-Triggered and Time-Triggered scheduling, independent tasks, task graphs, and runnables. Verifies system-wide timing chains across tasks, networks, and CPUs.

Customizable System Modeling: Enables the modelling of high-level communication layers, run-time environments, and applications using user-written Java plug-ins, allowing the simulation of complete embedded systems.

Benchmark Generation: Includes a benchmark generator to create random yet realistic Ethernet configurations. Useful for early-stage evaluation or studying network scalability.

Network-on-Chip Support: Compatible with Kalray and STMicroelectronics manycore architectures.

Seamless Data Exchange: Easily import/export configurations and simulation results through copy-paste, CSV, XLS, XML, YANG (as defined in the IETF/IEEE standards), Java plug-ins and industry-standard formats such as .dbc and .arxml.

Cross-Platform Compatibility: Runs on any platform supporting Java, with various licensing options including perpetual, time-limited, floating, or node-locked models.

Professional support and development of custom extensions.

API availability: RTaW-Pegase functionalities are also available through the Pegase Java library for integration into your own programs.

RTaW-Pegase automatically detects critical scenarios that cause maximum communication delays or excessive memory utilization in switches. By visualizing these scenarios in a Gantt diagram, you can easily identify network bottlenecks.

Contact the product manager to request a demo and an evaluation period.

Learn about the TSN standards and how to design efficient TSN networks.

Unified Modeling and Simulation for Networks and Real-Time Software in a Single Platform.

- 2024/10: A joint work with BMW entitled ‘Automotive System Requirements on Traffic Shaping’ was presented at the TSN/A Conference in Stuttgart on October 1-2, 2024. This study compares CBS and ATS traffic shapers, focusing on latency and memory utilization in a BMW pre-series vehicle. Download presentation slides.

- 2024/03: At the Automotive Ethernet Congress in Munich (March 5-7, 2024), we presented ‘How DDS and TSN Can Help Manage a Flexible In-Vehicle Network Architecture: Paving the Way to Software-Defined Networking.’ This presentation was part of a collaborative effort with our technology partner, Real-Time Innovations. Download presentation slides. Watch recorded webinar with RTI.

- 2023/09: The presentation ‘What are the Key Differences Between Asynchronous (ATS) and Credit-Based (CBS) Shapers?’ was delivered at the TSN/A Conference on September 27-28 in Ludwigsburg, Germany, in collaboration with Ethernovia. Download presentation slides.

2023/06: RTaW-Pegase V4.5 now supports the Data Distribution Service (DDS) middleware, automating the mapping of DDS-defined QoS to TSN mechanisms.. Interested? Contact us for a demo. RTaW and RTI have partnered to provide DDS & TSN solutions for mission-critical systems.

2023/03: The presentation ‘Ethernet TSN in Aerospace Systems: Experimental Assessment of QoS Mechanisms’ was delivered at Aerospace Tech Week on March 29-30 in Munich.

- 2023/03: Joint work with Renault and R. Bosch titled “Strategies for End-to-End Timing Guarantees in a Centralized Software Defined Vehicle Architecture Combining CAN With TSN Backbone” was presented at the Automotive Ethernet Congress on March 21-23, 2023 in Munich. Download presentation slides.

- 2023/03: Collaborative work with Volvo Cars, presented at the Automotive Ethernet Congress on March 22-23, 2023 in Munich, discussing the need, challenges, and solutions for ensuring timing predictability in next-generation E/E architectures. Download presentation slides.

2022/07: Pegase supports exporting network parameters in YANG, a standardized format for configuring TSN devices. In collaboration with customers, RTaW has developed open-source YANG models open-source YANG models that are freely available. This presentation at the July 2022 plenary meeting of IEEE 802.1 TSN TG explores the use of a single YANG file including all network parameters.

2022/06: Joint work with Volvo Cars presented at the Automotive Ethernet Congress on June 1-2, 2022 in Munich. This study, titled “Signal-Oriented ECUs in a Centralized Service-Oriented Architecture: Scalability of the Layered Software Architecture” highlights some of the use-cases of the Pegase’s new Software-Defined Vehicle module. Download presentation slides.

2021/11: Leverage system-level modeling with the new Software-Defined Vehicles (SDV) module , enabling the description, simulation, visualization (via Gantt charts), and worst-case schedulability analysis of software components on multi-core processors. Contact the product manager for detailed specifications and a demo. Watch a short video on SdV in Pegase.

- 2021/10: “Do we really need TSN in Next-Generation Helicopters? Insights from a Case-Study”, is a joint study with Airbus Helicopters presented at the 40th Digital Avionics Systems Conference (DASC 2021), San Antonio, Texas, October 3-7, 2021. Download paper – Download presentation slides.

- 2021/07: the Network-Calculus corner: explore our latest publications presenting algorithmic complexity improvements, formal verification of (min,+) computation correctness in RTaW-Pegase and new worst-case analyses for AVB/CBS and Network-on-Chips, co-authored with our partner Onera.

- 2021/04: RTaW staff serves as editor of the TSN standard IEEE P802.1Qcw and secretary of the aerospace profile standard (IEEE P802.DP). RTaW also participates in the activities of the automotive profile.

2021/02: “QoS-Predictable SOA on TSN: Insights from a Case-Study” is a joint study with Renault on their SOA architecture FACE, was presented at Automotive Ethernet Congress 2021. In this study, Pegase automates the mapping of SOME/IP frames to TSN QoS mechanisms, ensuring that individual service timing requirements and system-wide memory usage constraints are met.

- 2020/09: Collaborative projects with BMW Group (E/E architecture design automation – Download presentation slides here) and NXP semiconductors (reliability using IEEE802.1CB – Download presentation slides here) were presented at the 2020 IEEE Standards Association (IEEE-SA) Ethernet & IP @ Automotive Technology Day, Munich, September 14-18, 2020.

2020/02: Joint work with Volvo Cars on cost- and safety-optimization of Ethernet-based communication architectures was presented at the Automotive Ethernet Congress, 12-13 February 2020@Westin Grand Munich. Download presentation slides here. The study utilized the Topology Optimizer (TOP) design assistant, a feature of Pegase’s TSN Generative Design module, which was demoed at our booth.

2019/10: At the TSN/A Conference 2019 on October 8-9 at the Maritim Hotel Bad Homburg, we showcased our latest innovations at our booth. This year’s highlights were the Topology-Stress-Test design assistant for informed early-stage design choices and the support of IEEE802.1CB for enhanced safety through frame replication.

2019/09: “Early-stage Topological and Technological Choices for TSN-based Communication Architectures, a collaborative study with Renault Group, was presented at the 2019 IEEE Standards Association (IEEE-SA) Ethernet & IP @ Automotive Technology Day, Detroit, Mi, September 23-25, 2019. The presentation introduces Renault Group’s high-performance Service-Oriented Architecture, FACE, and demonstrates RTaW’s Topology-Stress-Test approach to quantify and optimize the number of SOME/IP services supported by the FACE E/E architecture. Download presentation slides here.

- 2019/04: CertiCAN is an academic tool developed at Verimag Lab in Grenoble, France, leveraging the Coq proof assistant for the formal certification of CAN schedulability analysis results. It has been successfully applied to verify the correctness of the results delivered by the CAN analyzer in RTaW-Pegase. – download the paper published at IEEE RTAS and this more recent paper. This groundbreaking achievement demonstrates that proving result correctness is feasible in an industrial setting.

2019/03: Introducing the Topology Stress Test (TST)Ⓒ—a cutting-edge design space exploration function that empowers designers to make early-stage topological and technological decisions (speed, protocols, hardware) without full knowledge of communication requirements. Now available in RTaW-Pegase v3.4.5.

- 2019/03: A hybrid approach for verifying TSN networks, combining the speed of machine learning with the safety of worst-case analysis, was presented at the 15th IEEE International Workshop on Factory Communication System (WFCS2019), Sundsvall, Sweden, May 27-29, 2019. Download the conference paper here.

2019/02: We showcased our innovations at the Automotive Ethernet Congress in Munich on February 13-14, 2019. Our workshop, titled ‘Automating the Design of In-Vehicle Ethernet Networks in 2020 and Beyond: The Beginning of the Centaur Era?’, attracted strong engagement from 45 participants. The discussion focused on how generative design and AI will transform the future of in-vehicle network design.

- 2019/01: Machine learning algorithms drastically accelerate the design space exploration of TSN networks. Download technical report here.

- 2018/10: We exhibited at the 2018 IEEE Standards Association (IEEE-SA) Ethernet & IP @ Automotive Technology Day in London, October 9-10, 2018. During the conference, we presented a study titled ‘Insights into the Performance and Configuration of TCP in Automotive Ethernet Networks’. RTaW-Pegase now provides full support for TCP over TSN. Download presentation slides here.

- 2018/09: we had a booth at the TSN/A Conference 2018, Stuttgart, September 26-27, 2018. We showcased the latest features of RTaW-Pegase for automotive users (e.g., DoIp protocol support) and industrial users (e.g., design of bridging strategies in hierarchical networks).

- 2018/06: New Java plugin infrastructure to extend RTaW-Pegase with your own models to simulate the functional behaviors of ECUs or high-level protocols, as easy as it gets.

- 2018/04: “Pre-shaping bursty transmissions under IEEE802.1Q as a simple and efficient QoS mechanism” is a joint work with Renault Group and Onera presented at the WCX18: SAE World Congress Experience (WCX018), Detroit, USA, April 10-12, 2018. Extended version published in SAE International Journal of Passenger Cars—Electronic and Electrical Systems, 11(3):2018. Download paper – Download presentation slides.

- 2018/02: “Insights on the performance and configuration of AVB and TSN in automotive networks” is a joint work with Renault Group presented at the 9th Embedded Real-Time Software and Systems Congress (ERTS 2018), Toulouse, France, January 31 – February 2, 2018. Download white paper here.

- 2018/02: “Computing Routes and Delay Bounds for the Network-on-Chip of the Kalray MPPA-256 Bostan Processor” is a joint study with Kalray and Onera presented at the 9th Embedded Real-Time Software and Systems Congress (ERTS 2018), Toulouse, France, January 31 – February 2, 2018. Download paper here.

- 2018/01: we had a booth at the Automotive Ethernet Congress in Munich, January 30-31, 2018 where we showcased for the first time ZeroConfig-TSNⒸ and presented joint work with Renault Group entitled: “Performance Assessment of Configuration Strategies for Automotive Ethernet”.

- 2017/10: “Experimental assessment of QoS protocols for in-car Ethernet networks” is a joint study with Renault Group and Onera presented at the 2017 IEEE Standards Association (IEEE-SA) Ethernet & IP @ Automotive Technology Day, San-Jose, October 31-November 2, 2017. Download presentation slides here.

- 2017/09: “Insights on the performance and configuration of AVB and TSN in automotive applications” is a joint study with Renault Group and Onera presented at the TSN/A Conference 2017, Stuttgart, September 20-21, 2017.

- 2017/02: We had a booth at the Automotive Ethernet Congress in Munich, February 7–8, 2017. We demoed use-cases of RTaW-Pegase on heterogeneous in-car communication architectures (CAN, CAN-FD and Ethernet) built on Autosar compliant communication stacks.

- 2017/01: Support Network-on-Chip for Kalray MPPA (worst-case analysis) and STMicroelectronics (simulation) manycore architectures,

- 2016/09: We had a booth at the IEEE-SA Ethernet & IP @ Automotive Technology Day (E&IP@ATD). This event about the evolution of Ethernet standards, technologies and applications in the automotive domain took place at the Mariott Rive Gauche in Paris on September 20-21, 2016.

- 2016/08: Underlying Network Calculus, the main timing analysis technique in RTaW-Pegase, is the (min,+) algebra. For people interested in the theory of Network-Calculus, we are glad to make the (min,+) Algebra Playground freely available on-line.

- 2016/01: RTaW had a booth at ERTS2016, January 27-29, 2016 in Toulouse, France. In the conference that took place along the trade-show, we presented two studies on in-car Ethernet networks and time-triggered Ethernet.

- 2015/11: TTEthernet (SAE AS6802) and time-triggered communication (eg. using IEEE1588) supported in RTaW-Pegase. This technical paper presented at ERTS2016 studies the interactions between the different classes of traffic in TTEthernet.

- 2015/08: RTaW and ONERA (the French Aerospace Lab) sign a scientific partnership in the field of timing verification for Ethernet networks. We are thrilled to strengthen our 5+ years collaboration with ONERA.

- 2015/04: “Timing verification of automotive Ethernet networks: what can we expect from simulation?“, study co-authored with Daimler Cars presented at the SAE World Congress, Detroit, USA, April 21-23, 2015. Slides are available here. See also the follow-up paper presented at ERTS2016.

- 2015/04: Study co-authored with Daimler Cars on how to best configure the SOME/IP SD protocol, presented at the SAE World Congress, Detroit, USA, April 21-23, 2015. White paper version available upon request. Slides are available here.

- 2015/03: Automotive Ethernet study led by Daimler Cars using the SOME/IP model of RTaW-Pegase: “Formal Analysis of the Startup Delay of SOME/IP Service Discovery“, presented at DATE 2015, Grenoble, France, March 9-13, 2015.

- 2015/02: RTaW had a booth at the Automotive Ethernet Congress in Munich, February 4–5, 2015, and showcased the new timing-accurate simulation engine.

- 2014/02: RTaW had a booth at the ERTSS congress in Toulouse, February 5–7, 2014. Two papers closely related to RTaW-Pegase were presented at the conference that takes place along with the trade-show – please see below,

- 2013/12: Modeling the frame scheduling on the sending end enables to compute much more precise bounds on the communication latencies with RTaW-Pegase, study co-authored with Onera and Thales Avionics presented at ERTSS2014,

- 2013/12: Proof-by-Instance for Embedded Network Design: From Prototype to Tool Roadmap, study co-authored with Onera and Inria presented at ERTSS 2014 on how to prove the correctness of frame worst-case response time calculations,

- 2013/08: Latest release includes NETAIRBENCH, a benchmark generator to create random but realistic switched Ethernet and AFDX configurations according to a set of user-defined parameters,

- 2013/07: Certifying the correctness of Network Calculus computations done in RTaW-Pegase, publication at EUCASS 2013 and second study published at ITP’2013,

- 2013/06: On the use of Deficit Round-Robin to facilitate incremental certification and mixed criticality scheduling, study presented at EUCASS 2013 co-authored with Onera and Thales Avionics,

- 2012/02: Comprehensive experimental study of RTaW-Pegase on hundreds of realistic AFDX configurations co-authored with Onera and Thales Avionics at ERTSS 2012,

- 2011/11: RTaW-Pegase received the best demo award at the Open Demo Session of Real-Time Techniques and Technologies of the 32nd IEEE Real-Time Systems Symposium,

- 2011/10: paper proving the correctness of some key algorithms implemented in RTaW-Pegase presented at the 1st International Workshop on Worst-case Traversal Time (download paper),

- 2011/10: publication at SAE Aerotech 2011 presenting experiments of RTaW-Pegase on real AFDX configurations (download paper – download slides).

Did we answer your questions?

Fill in the form to have an RTaW expert contact you to answer your questions and discuss any of your needs.