Software-Defined X

Speed-up Design Exploration, Optimization and Validation of Next-Generation Software-Defined Systems

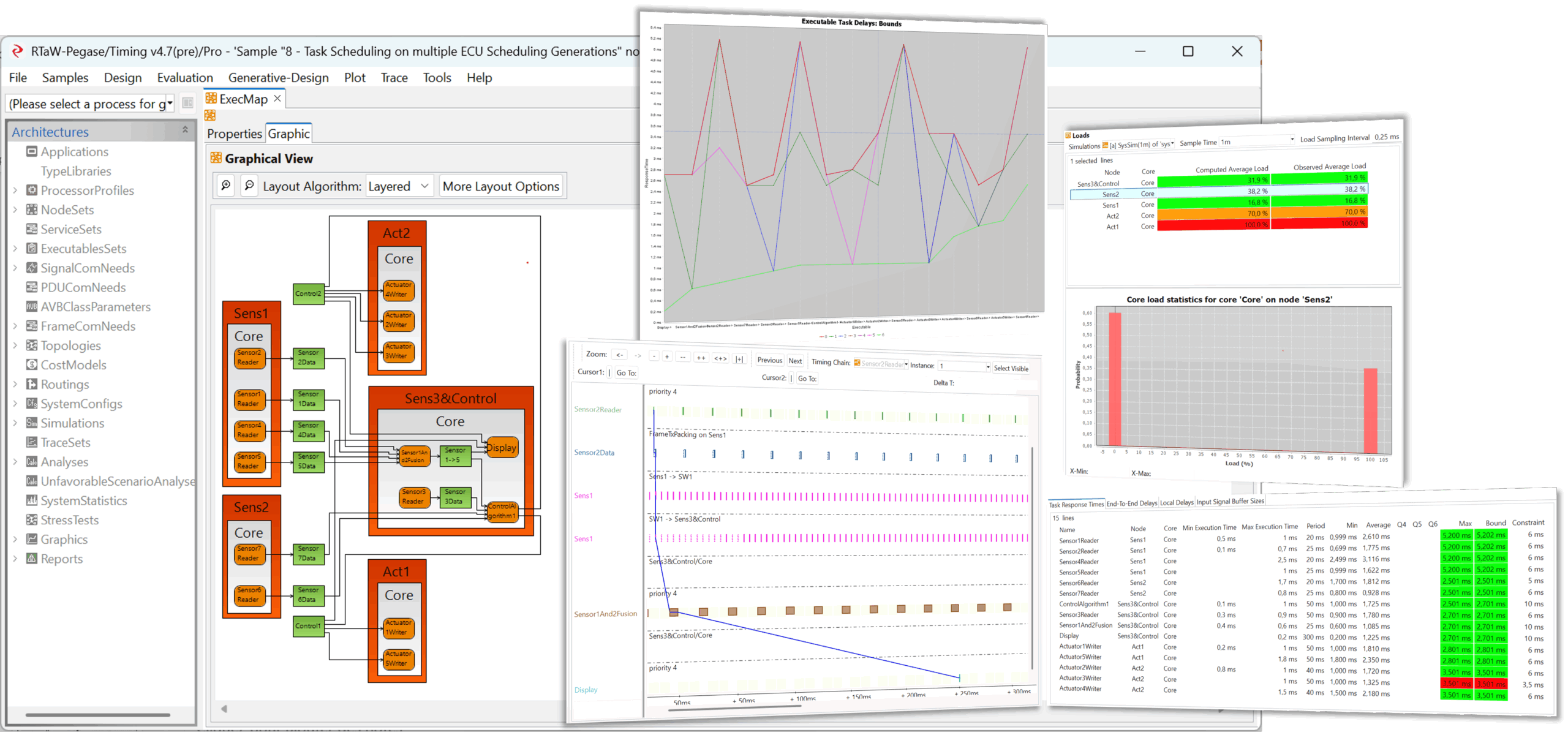

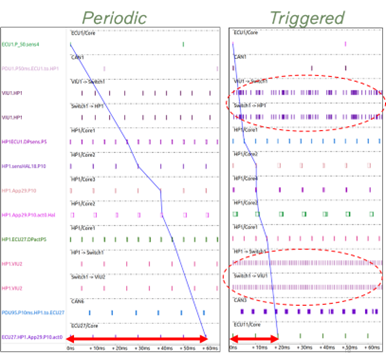

Software has become the key to innovation and is transforming entire industries. While the intensive use of software opens up vast opportunities for innovation, customization, and differentiation, it also introduces complex challenges for E/E architectures — challenges that RTaW-Pegase® Software-Defined X module addresses:

Validate Your Timing Constraints Before The First Line Of Code!

Testimonial

“The competition in the smart electric vehicle (EV) market necessitates the swift introduction of new features. This, in turn, demands a new generation of EEA (Electrical and Electronic Architecture) and communication technologies. The implementation of a brand-new tech stack results in challenges when addressing communication and task scheduling problems. RTaW’s SDV functionality enables us to model the temporal behavior of the vehicle and conduct insightful analysis of each activity chain. Throughout this process, the tool provides various scheduling models, state-of-the-art simulation algorithms, and, with RTaW’s robust support, assists us in identifying the traffic and CPU peaks of the system. Ultimately, it helps us pinpoint the appropriate solution. RTaW-Pegase plays a crucial role as a key tool in the development of next-generation EEA.”

Key Features